.

Recurso patrocinado Nos velhos tempos, havia uma CPU e os projetistas de chip amontoavam tudo em uma única CPU, o que fazia sentido para o maior número de clientes compensar o custo adicional de adicionar funcionalidade extra.

Qualquer tipo de computação especializada acabava sendo implementada em placas aceleradoras especiais rodando no barramento periférico ou implementada em software de nível superior rodando na CPU. E isso causava ineficiências óbvias, mas inevitáveis, devido à economia envolvida.

Aqui, na segunda década do século 21, a mesma economia e desejo por funções aceleradas estão acontecendo. Mas, em vez de fazê-lo na placa-mãe, é mais provável que eles funcionem dentro de um soquete, que é mais como uma placa-mãe e, de muitas maneiras, um sistema independente por si só.

Atualmente, as CPUs não têm apenas vários núcleos, mas hierarquias aninhadas de clusters de núcleos com suas próprias regiões de memória NUMA distintas. Algumas formas específicas e mais genéricas de aceleração são gravadas diretamente nos núcleos, assim como nos antigos processadores de núcleo único.

Mas, graças às incríveis densidades de transistor de chip e às técnicas de empacotamento de chiplet disponíveis hoje, outras formas de aceleração não são empurradas para o barramento PCI-Express, longe dos núcleos e da memória principal. Em vez disso, eles são implementados fora dos núcleos, mas nos próprios chiplets complexos do núcleo ou em chiplets distintos que estão interconectados dentro do pacote do soquete.

Até certo ponto, todas as CPUs de servidor modernas têm uma mistura de computação padrão de número inteiro e ponto flutuante nos núcleos e outros tipos de computação nas regiões não centrais do pacote. E, portanto, ao comparar processadores de diferentes fornecedores, é importante não apenas contar núcleos e velocidades de clock e o desempenho de número inteiro e ponto flutuante resultante nos benchmarks padrão do setor da SPEC. Você deve observar cargas de trabalho específicas e até que ponto os aceleradores dentro dos núcleos, bem como aqueles fora dos núcleos, trabalham em conjunto para aumentar o desempenho do aplicativo no mundo real.

Uma cornucópia de aceleradores

Ao longo dos anos, a Intel tem adicionado um número maior de aceleradores mais diversos às suas arquiteturas de CPU de servidor Intel® Xeon® e Intel® Xeon® SP. Isso foi impulsionado pelas necessidades de aplicativos específicos que a Intel direcionou para aumentar sua pegada Xeon e Xeon SP além da computação de uso geral no datacenter executando aplicativos escritos em C, C++, Java, Fortran, Python, PHP e outras linguagens. Em alguns casos, a mudança da computação do datacenter para adjacências, como virtualização de função de rede (NFV) ou armazenamento – onde os ASICs personalizados foram substituídos por CPUs X86 – levou à adição de aceleradores específicos. O mesmo se aplica aos espaços de simulação e modelagem de HPC e treinamento e inferência de IA.

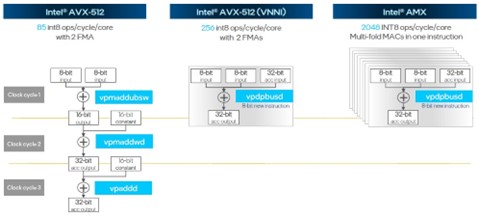

Como as GPUs foram redesenhadas para suportar o vetor pesado e a matemática de matriz usada em aplicativos HPC e AI, e ASICs personalizados foram inventados para impulsionar o desempenho ainda mais do que as GPUs, a Intel (entre outros fabricantes de CPU de servidor) engordou os mecanismos vetoriais e permitiu para oferecer suporte a dados inteiros e de ponto flutuante de menor precisão para puxar parte desse trabalho de HPC e IA de volta para a CPU. E em processadores mais recentes, unidades matemáticas de matriz projetadas especificamente para acelerar a matemática específica de matriz de baixa precisão comumente usada na inferência de IA (e às vezes no treinamento) também estão sendo adicionadas ao complexo de computação.

Com os núcleos “Golden Cove” usados no “Sapphire Rapids” Processadores escaláveis Intel® Xeon® de 4ª geração da Intela unidade matemática AVX-512 existente foi expandida para incluir suporte para acelerar determinados algoritmos matemáticos comumente executados pelo software vRAN executado em estações base de rede 5G.

Os núcleos Golden Cove também trazem uma nova unidade Intel Advanced Matrix Extensions (AMX), que permite que matrizes maiores sejam adicionadas ou multiplicadas em uma única operação e que fornecem muito mais rendimento do que executar operações inteiras de precisão mista no vetor Intel AVX-512 unidade.

Fig1: Sapphire Rapids Vector Matrix Rendimento

As unidades matemáticas Intel AVX-512 e Intel AMX em cada núcleo podem ser usadas simultaneamente – não é uma proposição ou/ou. Mas, claramente, para matrizes relativamente pequenas, o desempenho INT8 da unidade Intel AMX, que oferece um aumento de 8X na taxa de transferência bruta, será atraente, principalmente para (mas não limitado a) trabalho de inferência de IA. E como o lugar natural para fazer a inferência de IA é dentro da CPU onde os aplicativos estão sendo executados, a adição do acelerador Intel AMX ajudará a Intel a proteger seu território de inferência de IA. A maior parte da inferência de IA ainda é feita em CPUs hoje, e a Intel gostaria de mantê-la assim.

Em breve, faremos um mergulho mais profundo na execução de inferência de IA nativamente nas CPUs Sapphire Rapids e falaremos mais genericamente sobre os benefícios de desempenho desses e de outros aceleradores.

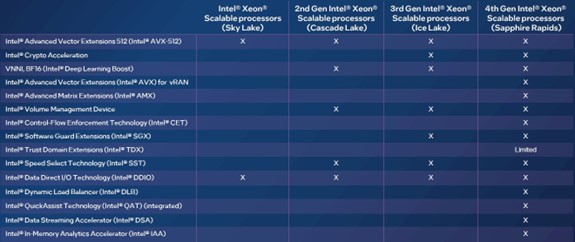

Antes de entrarmos em alguns dos exemplos de aumento de desempenho dos aceleradores Intel, seria útil mostrar toda a cornucópia da aceleração, que não está limitada às unidades de matriz Intel AMX e às unidades vetoriais Intel AVX-512 no Xeon SP core. Veja como a variedade de aceleradores cresceu ao longo das quatro gerações de processadores Xeon SP:

Fig2: Aceleradores Sapphire Rapids

As unidades vetoriais Intel AVX-512 existem desde 2015, e só agora a AMD está suportando uma funcionalidade equivalente em seus processadores Epyc 9004 “Genoa”. O mesmo ocorre com o suporte de meia precisão BF16 e FP16 nas unidades Intel AVX-512, que a Intel colocou na linha Xeon SP em 2019 e que aumentou a taxa de transferência de inferência de IA.

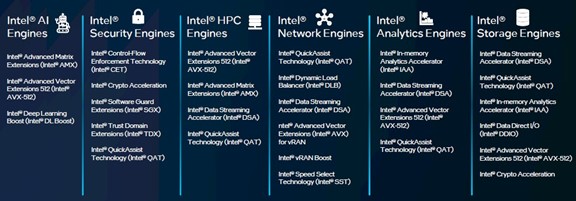

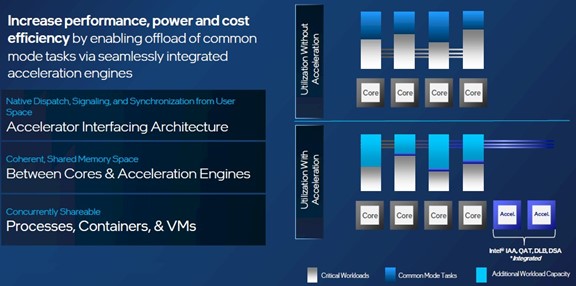

Para muitas cargas de trabalho, uma combinação de aceleradores é usada para aumentar o desempenho geral de um aplicativo ou do software de sistema que o sustenta. E, para esse fim, a Intel agrupa essas combinações de aceleradores para tipos específicos de cargas de trabalho no que chama de Intel Accelerator Engines.

Este é o nível de abstração que é, talvez, mais útil para empresas que avaliam CPUs de servidor e como a aceleração pode aumentar o desempenho ao mesmo tempo em que libera núcleos para fazer mais do processamento atual em qualquer carga de trabalho ou assumir trabalhos adicionais e distintos.

Fig3: Mecanismos Aceleradores Intel

O desempenho das cargas de trabalho impulsionadas por esses mecanismos aceleradores dependerá, é claro, das especificidades. Mas, conceitualmente, aqui está como a aceleração funciona em cada caso para maximizar a eficácia de cada núcleo em uma CPU Sapphire Rapids:

Fig4: Eficácia principal do Sapphire Rapids

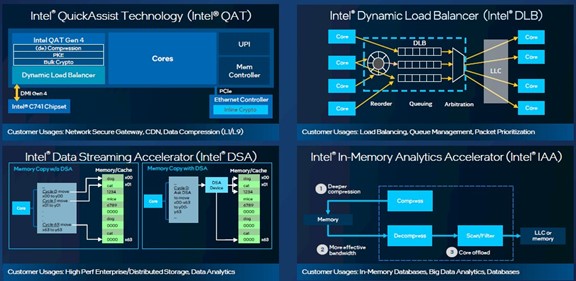

Algumas funções são aceleradas no núcleo e algumas são aceleradas fora do núcleo nessa mistura de motores aceleradores. O efeito líquido é que o Xeon SP resultante se comporta como uma CPU com muito mais núcleos. Novamente, tudo depende de quais funções estão sendo aceleradas. Além das unidades Intel AVX-512 e Intel AMX nos núcleos, aqui estão os esquemas de quatro dos importantes mecanismos de aceleração off-core:

Fig5: Sapphire Rapids QAT-DLB-DSA-IAA

Agora, para algumas provas sobre o aumento de desempenho resultante do uso de aceleradores não essenciais.

Vamos começar com o acelerador da tecnologia Intel Quick Assist, ou Intel QAT, que executa compactação e descompactação de dados, bem como criptografia e descriptografia. Executando o gateway seguro NGINX, foram necessários 84% menos núcleos para executar este software quando acelerado pelo Intel QAT do que executando o NGINX diretamente da caixa em um 4 Gen Xeon SP sem o Intel QAT ativado. Este teste foi feito em um servidor de dois soquetes usando processadores Xeon SP-8490H de 60 núcleos, o que significa que o que levou 120 núcleos para rodar sem Intel QAT levou apenas 19 núcleos com Intel QAT. Isso liberou incríveis 101 núcleos, de acordo com os testes da Intel.

O Intel Dynamic Load Balancer, ou Intel DLB para abreviar, faz exatamente o que você pensa: ele equilibra a carga de dados entre núcleos e interfaces de rede para evitar que a movimentação de dados atinja o congestionamento. Usando o gateway de entrada do Istio como uma carga de trabalho de microsserviços, a latência para ingestão de dados foi até 96% menor com o Intel DLB ativado e manteve a mesma taxa de transferência do Istio em execução com o Intel DLB desativado. Este teste foi executado em uma máquina de dois soquetes usando processadores Xeon SP-8480+ de 56 núcleos.

O Intel Data Streaming Accelerator, ou Intel DSA, otimiza a movimentação de dados de streaming e as transformações de dados. Em um servidor de dois soquetes baseado em processadores Xeon SP-8490H de 60 núcleos com Intel DSA ativado, as operações de E/S por segundo foram 1,7 vezes maiores do que em uma máquina equipada apenas com a Intel Storage Acceleration Library. É como ter uma máquina com 204 núcleos sem Intel DSA.

E, finalmente, o acelerador Intel In-Memory Advanced Analytics, abreviado para Intel IAA, aumenta o desempenho de primitivas analíticas, cálculos CRC e compactação e descompactação de dados comumente usados em bancos de dados e armazenamentos de dados. Com o Intel IAA ativado, o banco de dados de código aberto RocksDB foi capaz de processar 2,1 vezes mais transações do que a mesma máquina com o Intel IAA desativado e usando a compactação de dados Zstd que faz parte do RocksDB. Este teste foi realizado usando um par de processadores Xeon SP-8490 de 60 núcleos. Isso é como ter uma máquina com 252 núcleos sem Intel IAA.

Tudo isso significa que a Intel não está se preocupando com a contagem de núcleos tanto quanto você pensa que deveria.

Patrocinado pela Intel.

.