.

Paris Hilton está esclarecendo sua posição política – ou melhor, sua candidata presidencial de 2016.

Em seu novo livro, “Paris: as memórias”, a estrela da realidade e herdeira diz que na verdade não votou em Donald Trump, apesar de alegando ter feito dias depois de vencer a eleição de 2016.

“Quando fui questionado em uma entrevista, fingi que votei em Donald Trump porque ele era um velho amigo da família e dono da primeira agência de modelos com a qual assinei – e quando saí para ir para outra agência, ele ficou furioso e me intimidou pra caralho no telefone”, escreve Hilton em um trecho do livro reimpresso por Pessoas. “A verdade é ainda pior: eu não votei nada.”

De acordo com o trecho, a revelação de Trump aparece em uma lista de coisas das quais Hilton diz que “não se orgulha”.

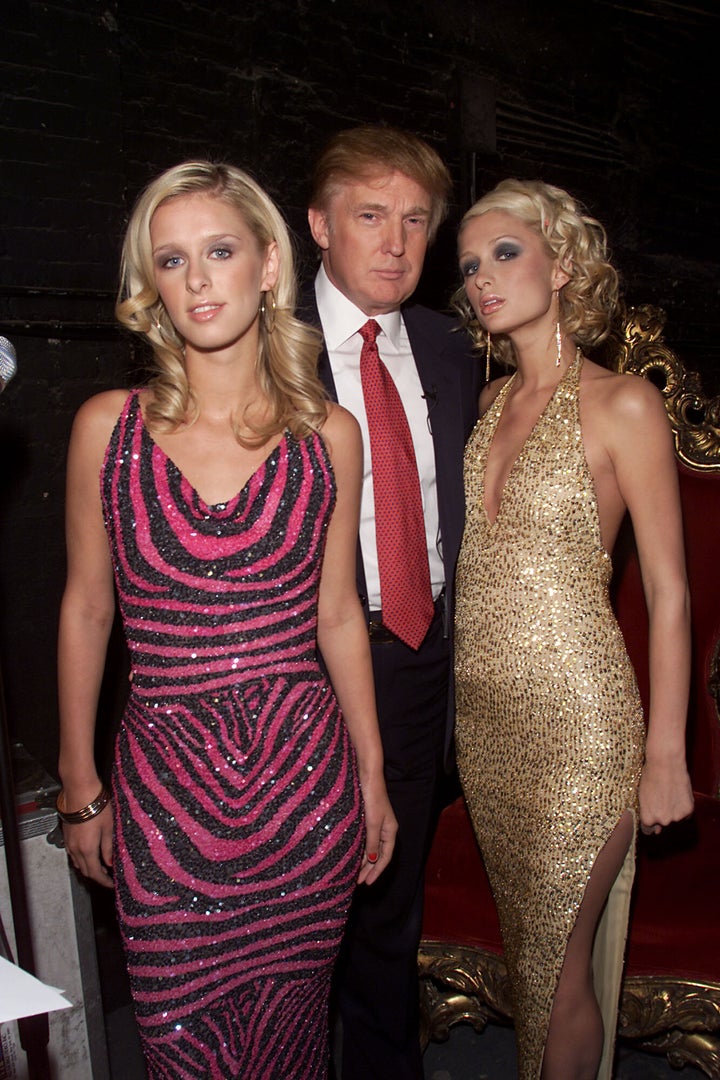

Hilton ― cujos pais, Rick e Kathy Hilton, foram alinhados de perto com a família Trump por décadas ― descreveu Trump como “um homem muito bom” em entrevista à CNBC meses antes das eleições de 2016.

Neilson Barnard via Getty Images

“Na TV, as pessoas gostam de dizer coisas sobre certas pessoas, mas na verdade ele é uma pessoa muito doce”, disse Hilton na época. “Eu gosto muito dele.”

Ela reiterou essa postura quando questionada pelo programa de notícias australiano “O projeto” se ela tivesse votado em Trump cerca de uma semana após o fim da corrida à Casa Branca de 2016.

“Eu o conheço desde que era uma garotinha. Então, sim”, disse ela.

Hilton começou a mudar de tom menos de um ano depois, no entanto, admitindo em uma entrevista de 2017 da Marie Claire que na verdade ela não votou em Trump, a quem ela elogiou como “um empresário incrível” que “sempre foi tão legal, tão respeitoso e doce”.

Em outra parte do bate-papo, ela passou a descartar a história de Trump de observações depreciativas sobre as mulheres, incluindo ela mesma. “Já ouvi caras dizerem as coisas mais loucas de todas, porque estou sempre perto deles e os ouço falar”, disse ela.

Arquivo Frank Micelotta via Getty Images

Hilton foi recentemente chamada por seu apoio anterior a Trump em um artigo do Daily Beast de 2022que questionou suas tentativas de recuperar a atenção com uma série de novos projetos, incluindo o livro.

“Por que a Hollywood liberal está tão empenhada em colocá-la de volta aos holofotes?” escreveu Kyndall Cunningham.

Hilton notavelmente tomou medidas para se distanciar de Trump ultimamente. Em “Paris: The Memoir”, ela relembra sua decisão de fazer um aborto aos 22 anos, escrevendo: “As mulheres precisam controlar seu destino reprodutivo”.

Falando para a revista Glamour no mês passado, Hilton supostamente “se irritou[d]” quando foi sugerido que Trump, que apoiou a decisão da Suprema Corte de 2022 que anulou o direito ao aborto, é um “amigo próximo da família”.

“Não mais”, disse ela à publicação.

.