.

Comente A AMD está a apenas algumas semanas de revelar a próxima fase de seu portfólio de datacenter em um lançamento em San Francisco.

Tendo exibido seus mais recentes chips de datacenter mainstream em novembro, o designer do processador Epyc deve revelar seus próximos componentes especializados para nuvem, IA e computação técnica.

Portanto, antes de a CEO Lisa Su subir ao palco em 13 de junho, pensamos em examinar todos os produtos que esperamos que a AMD anuncie.

AMD enviará uma APU para o datacenter

Dado todo o hype em torno da IA generativa ultimamente, vamos começar com a unidade de processamento acelerado (APU) da AMD, o Instinct MI300A.

As APUs têm sido um dos pilares da linha de PCs e eletrônicos embarcados da AMD: elas apresentam um cluster de CPU com um processador gráfico integrado e podem lidar com uma combinação de cargas de trabalho de computação e processamento paralelo.

Em vez de computação pessoal, o MI300A terá um foco muito diferente: AI/ML e computação de alto desempenho. Na verdade, agora sabemos que o chip será os cerebros do futuro supercomputador El Capitan do Laboratório Nacional Lawrence Livermore dos Estados Unidos.

O MI300A também é diferente de qualquer APU que vimos da AMD até hoje – bem, exceto por um. Em 2017, Intel e AMD uniram-se para emparelhar uma matriz de CPU Intel com uma GPU AMD Radeon e memória HBM2. O MI300A seguirá um padrão semelhante, mas em vez dos núcleos de CPU da Intel, ele usará os núcleos da família Zen internos da AMD e oferecerá muito mais desempenho de GPU.

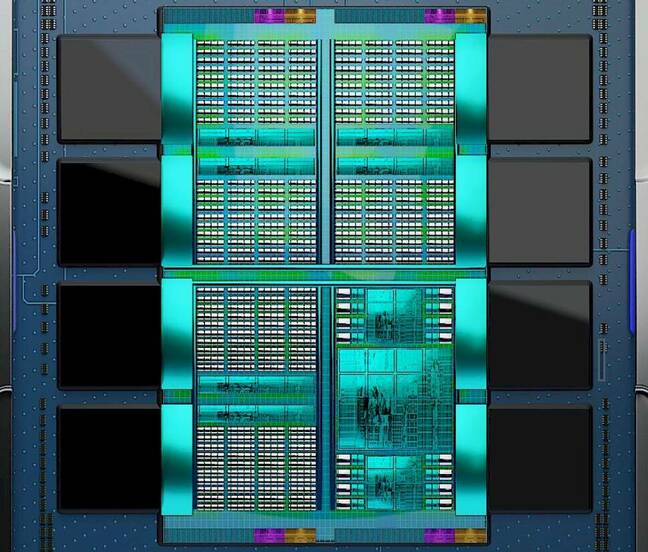

A AMD tem sido bastante discreta até agora, mas revelou que o MI300A contará com 24 núcleos Zen 4, 128 GB de memória HBM3 e, pelas renderizações, o que parece ser seis matrizes de GPU CDNA.

Curiosamente, parece que a AMD pode não estar usando a mesma arquitetura de chiplet encontrada na série Epyc 4 Genoa do ano passado. As renderizações do MI300A parecem mostrar duas matrizes complexas de núcleo (CCDs) – o que a AMD chama de chiplets de CPU. A julgar pela imagem, que pode estar ofuscada ou simplesmente errada, a AMD pode realmente usar dois CCDs de 16 núcleos, como os que esperamos encontrar em Bergamo – mais sobre isso depois – em vez de dois CCDs de 12 núcleos. CCDs duplos de 16 núcleos seriam muitos núcleos, mas não é incomum que a AMD desabilite núcleos em seus CCDs, reduzindo o número de trabalho de 32 para 24.

Se este for de fato o caso, a AMD pode ter feito isso para manter um clock de núcleo mais alto para o orçamento de energia fornecido.

A AMD revelou que o chip oferecerá um aumento de 8x no desempenho de AI e uma melhoria de 5x no desempenho por watt em comparação com o MI250X, que sustenta o supercomputador 1.1 exaFLOPS Frontier. Uma parte decente dessa melhoria provavelmente vem da adição do suporte do FP8 desta vez. A precisão mais baixa geralmente resulta em desempenho geral mais alto em cargas de trabalho de IA em detrimento da precisão reduzida.

Considerando que um único Epyc 4 pode consumir mais de 400 W e o MI250X tem um orçamento de energia de cerca de 600 W, é seguro assumir que o MI300A não será econômico quando se trata de energia. Nossos colegas em A Próxima Plataforma estimativa neste mergulho profundo que o chip fornecerá algo em torno de 3 petaFLOPS de desempenho FP8 em um orçamento de energia de 850 W. Isso tornaria o chip menos faminto por energia do que o superchip Grace-Hopper da Nvidia, e também não tão poderoso.

Espera-se que o MI300A seja apenas um dos vários SKUs para levar o nome. Esperamos que haja uma configuração somente de GPU. Olhando para as renderizações do pacote, parece que a AMD poderia colocar mais duas matrizes de GPU lá, uma vez que os CCDs e a matriz de E/S foram removidos.

No que diz respeito às opções de soquete, o MI300A parece suportar pelo menos quatro configurações de soquete. Pelo que vimos do El Capitan, parece que cada nó contará com quatro APUs.

Do ponto de vista do mercado, ninguém mais tem um chip igual. O Falcon Shores XPU da Intel deveria apresentar uma configuração semelhante de CPU+GPU, mas esse projeto foi enlatado em favor de uma GPU regular. Isso deixa a Nvidia Superchip Grace-Hopper como principal concorrente da AMD.

Com isso dito, eles são bestas muito diferentes. O MI300A está se preparando para ser uma APU adequada com comunicações diretas die-to-die e um pool compartilhado de memória. O Grace-Hopper difere por unir um processador de CPU compatível com Arm de 72 núcleos com uma GPU H100 de 96 GB usando a interconexão NVLink-C2C da Nvidia.

A AMD desafiará a Ampere com uma CPU própria focada na nuvem

Desde a introdução dos primeiros processadores Epyc da AMD em 2017, os chips tiveram uma adoção constante por provedores de nuvem que priorizam a densidade do núcleo em detrimento do desempenho do núcleo individual.

Ao longo dos anos, vimos os chips da AMD passarem de 32 núcleos para 64 e, mais recentemente, para 96. No entanto, a partir de 2020, um concorrente chegou, prometendo contagens de núcleos ainda maiores. Compatível com Ampere’s Arm processadores Altra ofereceu 80 e eventualmente 128 e 192 núcleos e foram direcionados a provedores de nuvem, que os engoliram.

A aritmética era bastante simples: mais núcleos de CPU significavam que os clientes poderiam empacotar confortavelmente mais VMs e contêineres em uma única caixa. Para atender a esse segmento de mercado emergente, a AMD revelou que estava trabalhando em um chip próprio otimizado para o núcleo. Em seu evento Accelerated Data Center no final de 2021, a AMD apresentou um processador de 128 núcleos chamado Bérgamo que foi projetado especificamente para cargas de trabalho nativas da nuvem.

Esperamos que o chip, inicialmente planejado para o início deste ano, seja um dos grandes anúncios da AMD no evento de junho. Então, aqui está o que sabemos sobre o chip até agora.

A Bergamo apresentará uma nova variação do núcleo Zen 4 da AMD chamada Zen 4c. Também sabemos que Bergamo apresentará uma configuração principal diferente do Epyc 4 Genoa. Em vez de 12 CCDs de oito núcleos, entendemos que o Bergamo apresentará oito CCDs de 16 núcleos para atingir sua meta de 128 núcleos.

Esse arranjo de núcleo mais denso nos diz que o núcleo Zen 4c provavelmente será reduzido em comparação com os núcleos Zen 4 completos encontrados em Gênova. Se tivéssemos que adivinhar, a AMD provavelmente está diminuindo o já grande cache L3 – cada CCD tem 32 MB no Genoa – para abrir espaço para os núcleos extras. Embora isso seja um palpite, e a AMD pode ter removido funcionalidades adicionais de baixa utilidade para clientes em nuvem.

Também não sabemos muito sobre o tipo de desempenho que podemos esperar dos novos núcleos Zen 4c do chip, mas podemos fazer algumas suposições. Se a AMD seguir o exemplo da Ampere, podemos esperar que a Bergamo priorize velocidades de clock consistentes em vez de aumentar as frequências. Em outras palavras, clocks base relativamente altos, mas não muito ou nada em termos de boost clocks.

Também suspeitamos que a AMD manterá metas de potência de design térmico (TDP) semelhantes para o chip, como vimos no Epyc 4, colocando-o na faixa de 360-400W. Isso por si só exigiria uma escala de frequência mais conservadora do que nas partes Epyc anteriores devido à maior contagem de núcleos do chip.

Uma área em que o Bergamo será diferente dos chips nativos da nuvem da Ampere é o suporte para multithreading simultâneo. Um único chip Bergamo terá 128 núcleos e 256 threads. Além do multi-threading, vale lembrar que esses núcleos AMD ainda são x86-64. Isso significa que, se o seu aplicativo for executado em um Epyc ou Xeon hoje, ele deverá ser executado no Bergamo sem problemas. Sim, você pode recompilar ou portar software, se possível, mas você sabe o que queremos dizer.

O mesmo nem sempre pode ser dito do Ampere Altra – ou do Graviton da AWS – apesar do esforço considerável da Arm para certificar sistemas e instâncias de nuvem em execução em seu conjunto de instruções. A migração de cargas de trabalho para esses chips nem sempre é garantida.

Apesar disso, a AMD não terá a vantagem de ser pioneira aqui. O mercado de silício otimizado para nuvem ficou consideravelmente mais aquecido nos últimos anos, e Bergamo terá que enfrentar não apenas a última geração de CPUs Arm da Ampere, mas também as próprias peças otimizadas para núcleo da Intel em breve.

A Ampere recentemente exibiu sua Família AmpereOne de chips, que chegará a 192 núcleos. Enquanto isso, a Intel prometeu um Xeon de 144 núcleos chamado floresta de serra para o primeiro semestre de 2024. Portanto, embora a AMD vença a Intel no mercado, ela não terá uma liderança central sobre seu rival de longa data.

AMD Genoa-X vai acumular no cache

Bergamo não é o único chip que esperamos ver no evento de junho da AMD. Espera-se que a empresa lance sua segunda geração de processadores “técnicos”, codinome Genoa-X.

Esses chips são projetados para uma variedade de aplicativos de computação técnica, como dinâmica de fluidos computacional, bancos de dados e outras cargas de trabalho com uso intensivo de largura de banda.

Introduzido em 2021 com o anúncio de Milão-X, os chips apresentam uma técnica de empacotamento avançada que coloca SRAM adicional sobre os CCDs do chip. Usando esse método, a AMD conseguiu empacotar 64 MB adicionais de cache L3 em cada matriz para um total de 768 MB de L3 em seu chip de especificação superior.

Conforme informamos em junho passado, o Genoa-X aumentará isso para mais de 1 GB de L3 por soquete. Isso faz sentido, já que Gênova tem quatro CCDs a mais que Milão, mas também sugere que a AMD não está fazendo nada de especial desta vez.

Com 96 MB de L3 por CCD e 12 CCDs nos chips Genoa-X de 96 núcleos da AMD, isso resulta em 1.152 MB de cache L3 por soquete.

No entanto, como nosso site irmão A Próxima Plataforma encontrado, o preço mais alto associado a esses chips nem sempre é correspondido por seu desempenho. Apesar disso, a AMD já demonstrou aumentos significativos de desempenho em determinadas cargas de trabalho, como o teste VCS da Synopsys.

Mais por vir

O evento de junho da AMD está se preparando para ser grande, mas os negócios ainda não estão prontos para revelar tudo. Notavelmente, ele tem pelo menos mais um lançamento de CPU previsto para este ano: Siena.

Embora ainda não saibamos muito sobre Siena, a AMD disse o produto tem como alvo os mercados de edge e telco, prioriza o desempenho por watt e contará com até 64 núcleos.

Como já fizemos anteriormente relatado, a Intel detém uma influência descomunal sobre o mercado de ponta, onde a grande maioria dos sistemas “de ponta” está executando processadores Xeon. No entanto, teremos que esperar até o segundo semestre de 2023 para ver o quão atraente o concorrente da AMD no espaço realmente é. ®

.