.

2023 é um ano histórico na indústria de semicondutores. Isso ocorre porque a TSMC e a Samsung Foundry estão enviando chips feitos usando seus respectivos nós de processo de 3nm. Quanto menores os nós do processo, menor o tamanho do recurso do chip, o que significa transistores menores e maiores contagens de transistores. Quanto mais transistores em um chip, mais poderoso e eficiente em termos de energia é esse chip. A Apple supostamente amarrou toda a produção de 3nm de primeira geração da TSMC e o A17 Bionic de 3nm estreará no iPhone 15 Pro e iPhone 15 Ultra ainda este ano.

A TSMC iniciará a produção de 2 nm em 2025 com produção aprimorada de 2 nm a partir de 2026

Na sexta-feira, um novo relatório da publicação online de Taiwan MoneyDJ (via Wccftech) diz que a TSMC iniciará a produção em massa de chips de 2 nm a partir de 2025. Como é típico, uma versão aprimorada da produção de 2 nm chamada N2P começará em 2026, um ano após a produção de N2 de primeira geração. Isso ecoa o nome N3 para a atual produção de 3nm da TSMC e o nome N3P que a TSMC chamará de nó de 3nm aprimorado que deve estar disponível no próximo ano.

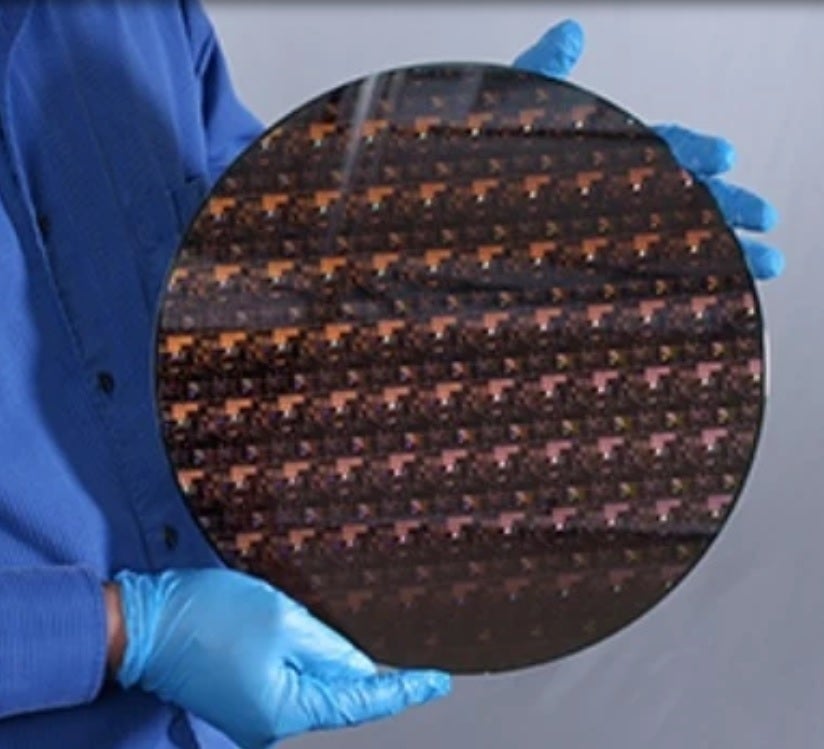

Wafers para produção de 3 nm custam cerca de US$ 20.000 cada

Diz-se que os rendimentos de N3 da TSMC estão melhorando e com wafers para produção de 3 nm supostamente custando US $ 20.000 por pop, os rendimentos crescentes são um sinal positivo. No entanto, A Apple verá esse aumento de preço em 3% ainda este ano. A Apple supostamente paga US$ 110 por cada chipset A16 Bionic de 4nm e o A17 Bionic de 3nm, que deve alimentar o iPhone 15 Pro e o iPhone 15 Ultra, pode custar US$ 150 para cada SoC.

O CEO da TSMC, CC Wei, disse estar confiante de que a TSMC estará pronta para produzir em massa chips de 2 nm até 2025. O relatório de hoje confirma a opinião de Wei e diz que a empresa está no alvo com seu cronograma de 2 nm.

Com sua produção de 2nm de segunda geração conhecida como N2P, a TSMC usará o que é conhecido como BSPD (backside power delivery). Isso permite que os transistores extraiam energia elétrica de um lado de um chip enquanto o outro lado será usado para conectar transistores com links de conexão de dados. Esta é a mesma tecnologia que a Intel usará na tentativa de recuperar a liderança do processo da TSMC e da Samsung Foundry, embora a Intel a chame de PowerVia.

A TSMC também começará a usar transistores gate-all-around (GAA) com sua produção de 2nm. Os transistores GAA têm contato com o canal em todos os quatro lados graças ao uso de nanofolhas horizontais colocadas verticalmente no chip. Isso reduz vazamentos e permite menor consumo de energia. Também aumenta a corrente do drive, levando a um melhor desempenho do chip.

A Samsung Foundry já está usando GAA para sua produção de 3nm, enquanto a TSMC continua a usar transistores FinFET em seus chips de 3nm. Os transistores FinFET cobrem apenas três lados do canal, o que resulta em mais vazamento. A Intel também planeja usar o GAA, que chama de RibbonFET.

A Intel é o curinga com seus planos de recuperar a liderança do processo até 2025

Gordon Moore, cujas observações levaram à criação da Lei de Moore em 1965, faleceu recentemente aos 94 anos de idade. Mas a Lei de Moore continua em vigor, embora seja mais sobre a tendência contínua de empacotar mais transistores em chips a cada dois anos, em vez de ver a contagem de transistores dobrar a cada dois anos.

Com uma participação de mercado de 17,3%, a Samsung fica atrás da fatia de 52,9% da TSMC no mercado de fabricação de chips. Alegadamente, a Samsung espera triplicar a capacidade de produção de seus chips mais avançados entre agora e 2027, na tentativa de reduzir essa lacuna de participação de mercado. E depois há a Intel. O curinga aqui, o CEO da empresa, Pat Gelsinger, diz que recuperar a liderança do processo da TSMC e da Samsung Foundry até 2025.

.