.

O conjunto de instruções de código aberto do RISC-V atraiu muita atenção nos últimos anos e não apenas aqui na Terra – uma equipe da ETH Zurique, na Suíça, afirma ter desenvolvido um microcontrolador de baixo consumo de energia e tolerante a falhas para cubesats baseado no arquitetura.

“Um dos principais desafios ao operar microcontroladores em ambientes adversos, como o espaço, são os distúrbios de evento único (SEU) induzidos por radiação, resultando em erros de computação”, escreveu a equipe em um artigo. Publicados essa semana.

Tradicionalmente, esse problema tem sido resolvido com o uso de chips de endurecimento por radiação desenvolvidos em nós de processo mais antigos. O antigo BAE RAD750 baseado em PowerPC é um excelente exemplo. Introduzido em 2001, foi fabricado em um nó de processo de 250 nm e duas décadas depois o chip ainda está em uso e voou em inúmeras missões e alimenta os rovers Curiosity e Perseverance e o Telescópio Espacial James Web.

Embora capaz de sobrevivendo com uma dose total entre 200 quilorads e um milirad, dependendo do nível de endurecimento por radiação, o chip não é exatamente o mais eficiente em termos de energia. De acordo com pesquisadores da ETH Zurich, ele tem capacidade de cinco watts de potência.

“Muitos satélites e cubesats menores estão sendo projetados e lançados. Eles não podem arcar com o grande orçamento de energia exigido pelos típicos SoCs confiáveis para o espaço, com poucos watts disponíveis para o sistema completo”, escreveram eles.

O chip Trikarenos baseado em RISC-V da equipe visa resolver isso com um design tolerante a falhas baseado na tecnologia de processo de 28 nm da TSMC, que a equipe diz ter “demonstrado tolerância aos efeitos destrutivos da radiação” e é tão eficiente quanto os designs anteriores.

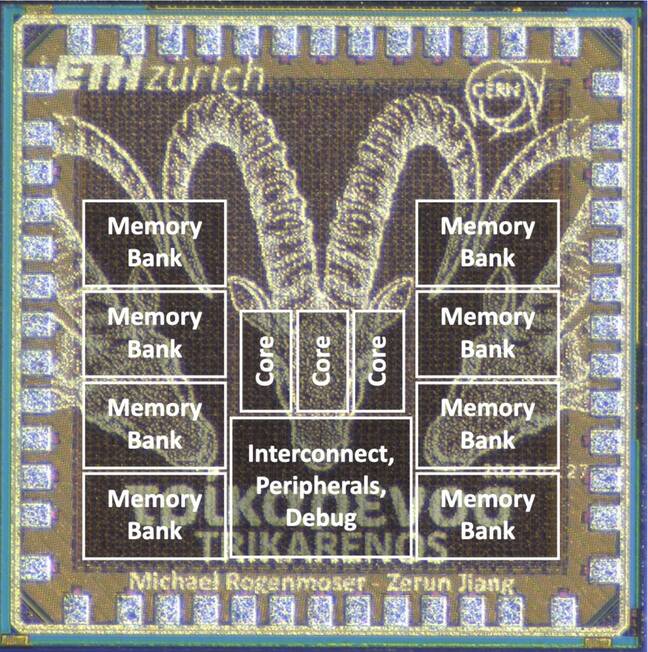

O Trikarenos da ETH Zurich usa um design de núcleo triplo para corrigir erros causados por partículas de alta velocidade no espaço. – Clique para ampliar

O chip em si é baseado em uma potência paralela ultrabaixa PULPismo design e possui três núcleos Ibex baseados em RISC-V com clock de até 270 MHz. Esses núcleos são alimentados por oito bancos SRAM com 256 KB de memória.

Para minimizar o risco de um evento único, o chip também apresenta diversas rotinas arquitetônicas, incluindo redundância integrada, memória de correção de erros e purificadores.

Embora um processador de três núcleos possa parecer um pouco estranho, na verdade ele serve a um propósito quando se trata de tolerância a falhas. Por padrão, o chip opera no chamado modo lock-step de três núcleos, no qual as operações são executadas simultaneamente em todos os três núcleos. No caso de um SEU corromper a saída de um núcleo, uma votação é realizada e a saída é corrigida – pense no Relatório Minoritário com lógica.

“Cuidado especial foi tomado para separar fisicamente os três núcleos Ibex entre si e a lógica restante, garantindo uma lacuna de 20 micrômetros com a lógica em torno de cada núcleo”, observaram eles no artigo.

Isto foi importante porque os projetistas precisavam garantir que o impacto de uma única partícula não pudesse afetar elementos semelhantes em dois núcleos separados.

Embora o design de núcleo triplo tenha uma vantagem em termos de tolerância a falhas e tratamento de erros, ele tem um custo de desempenho. No entanto, mesmo com todos os três núcleos executando as mesmas operações, os pesquisadores afirmam que o Trikarenos pode alcançar desempenho equivalente ao venerável RAD750, consumindo apenas 15,7 miliwatts de energia.

E para cenários onde a confiabilidade não é fundamental, os núcleos podem operar em paralelo, triplicando efetivamente o desempenho do chip, permitindo que cada um dos núcleos processe números independentemente um do outro.

Levando RISC-V para órbita e além

A ETH Zurich não é a primeira a propor uma peça baseada em RISC-V para voos espaciais. No ano passado nós aprendido que os núcleos de CPU compatíveis com RISC-V do SiFive alimentariam o computador de voo espacial de alto desempenho (HPSC) da NASA.

O sistema de computador está sendo desenvolvido em colaboração com SiFive e Microchip sob um contrato de três anos no valor de US$ 50 milhões. Quando concluída, espera-se que a peça se torne a espinha dorsal para futuras missões tripuladas e não tripuladas das agências espaciais.

No entanto, comparado ao Trikarenos, o HPSC será um pouco mais poderoso. De acordo com SiFive, a peça proporcionará uma melhoria de 100 vezes no desempenho em comparação com o RAD750 que ela substitui. Diz-se que esse chip possui 12 núcleos, oito baseados no design do processador vetorial X280 da SiFive e quatro núcleos de uso geral. ®

.