.

A AMD revelou um par de processadores Epyc voltados para aplicativos técnicos e em nuvem e planos detalhados para sua família de aceleradores Instinct MI300 durante seu evento Datacenter e AI em San Francisco.

O primeiro é um novo processador Epyc projetado com provedores de nuvem e hiperescaladores em mente. Com o codinome Bergamo, o chip contém até 128 núcleos por soquete e foi otimizado para uma variedade de cargas de trabalho em contêineres, afirma a AMD.

A AMD não é estranha a chips pesados. Desde o lançamento de seu Epycs de primeira geração em 2017, a empresa manteve uma liderança constante na contagem de núcleos sobre a rival de longa data Intel. No entanto, o Epyc de 128 núcleos da AMD não é voltado para a Intel – pelo menos ainda não – assim parece.

Em vez disso, a AMD posicionou o Bergamo como uma espécie de baluarte contra os produtos compatíveis com Arm da Ampere Computing. chips de data centerque tiveram ampla adoção entre cloud e hyperscalers desde que chegaram ao mercado em 2020. Hoje, todos os principais provedores de nuvem – com exceção da AWS, é claro – implantaram os chips da Ampere.

Com Bergamo, a AMD pretende recuperar parte desse terreno perdido. O fabricante de chips chegou ao ponto de se gabar de que o Bergamo é inigualável em configurações de soquete único ou duplo, pelo menos no benchmark SPECrate2017 Integer.

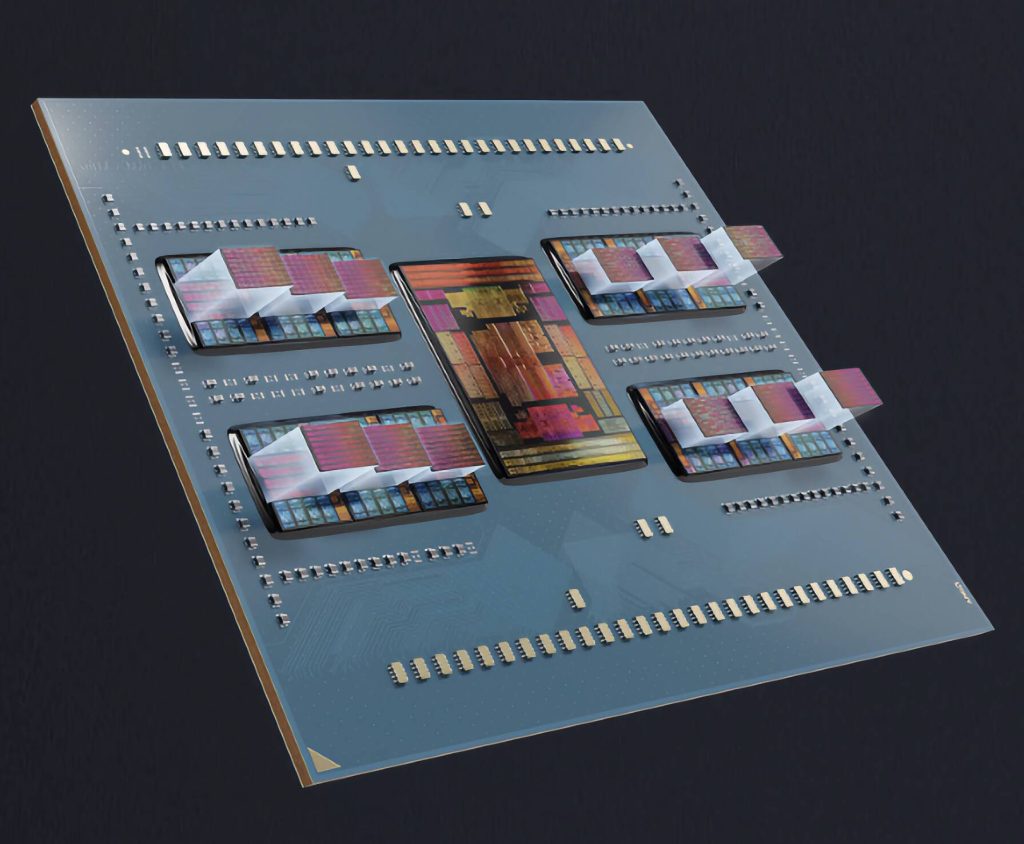

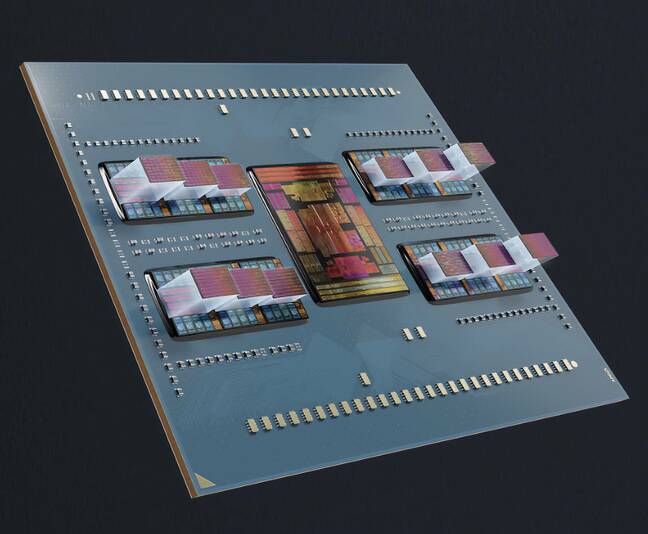

Espiar sob o enorme dissipador de calor revela um chip que na superfície se parece muito com os Epycs anteriores. Na verdade, você seria perdoado por pensar que isso era o mesmo que Roma ou Milão, até a matriz de E/S central e oito matrizes de complexo central (CCDs) circundantes.

Os processadores Bergamo Epyc da AMD apresentam 128 núcleos e 256 threads espalhados por oito matrizes complexas de núcleo

Apesar das semelhanças, Bergamo é uma fera muito diferente com o dobro de núcleos por CCD do Genoa em 16, e um design de núcleo totalmente novo chamado Zen 4c, onde o “c” presumivelmente significa nuvem.

“O Zen 4c é realmente otimizado para o ponto ideal de desempenho e potência, e isso é o que realmente nos dá uma densidade e eficiência energética muito melhores”, disse Lisa Su, CEO da AMD, em seu discurso de abertura. “O resultado é um design com área 35% menor e desempenho substancialmente melhor por watt.”

Esses núcleos também suportam multithreading simultâneo (SMT), algo que o Ampere tem se esquivou de, citando a imprevisibilidade do desempenho e as implicações de segurança como sua justificativa.

No entanto, em cargas de trabalho dimensionadas em contêineres, o SMT pode render dividendos, onde mais threads teoricamente devem permitir que a AMD alcance densidades maiores. Densidades três vezes maiores em cargas de trabalho em contêineres, de acordo com os benchmarks internos da AMD.

Infelizmente, a AMD não divulgou as velocidades de clock do chip ou a configuração de cache nos materiais que compartilhou conosco antes da palestra. Por causa disso, é difícil dizer quais concessões a empresa foi forçada a fazer para encaixar os núcleos extras.

Além da nova arquitetura de núcleo e chiplet de Bergamo, a plataforma tem muito em comum com Genoa. Ele suporta 12 pistas de memória DDR5, o mais recente PCIe 5.0, e pode ser configurado em configurações de soquete único ou duplo.

Uma vantagem notável que a AMD tem sobre o Ampere, pelo menos por enquanto, é o amplo suporte para o conjunto de instruções x86. Os clientes acostumados a executar cargas de trabalho em sistemas Intel e AMD não precisarão refatorar seus aplicativos para aproveitar a maior densidade de núcleo – algo que não é necessariamente verdade quando migrando para Arm.

Bergamo não será único nesta faceta particular por muito mais tempo. A Intel prometeu um Xeon otimizado para núcleo, com ainda mais núcleos para o início de 2024. O chip, codinome floresta de serracontará com até 144 núcleos de eficiência da empresa.

AMD torna-se técnico com outro X-chip

A AMD também revelou seu último chip X empilhado em cache, codinome Genoa-X, durante o evento.

O chip é voltado para aplicativos de computação de alto desempenho – o que a AMD gosta de chamar de cargas de trabalho técnicas – incluindo dinâmica de fluidos computacional, automação de design eletrônico, análise de elementos finitos, tomografia sísmica e outras cargas de trabalho sensíveis à largura de banda que beneficiam um carregamento de cache compartilhado.

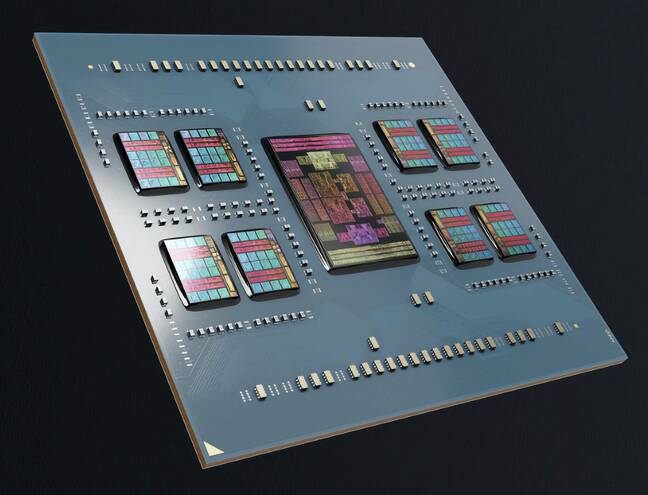

A CPU Genoa-X da AMD empilha blocos SRAM de 64 MB sobre cada um dos chips computacionais para um total de 1,1 GB de cache L3

Como o nome sugere, o chip é baseado na plataforma Genoa padrão da empresa, mas apresenta a tecnologia 3D V-Cache da AMD, que aumenta o cache L3 disponível empilhando módulos SRAM verticalmente em cada um dos CCDs.

A AMD diz que o Genoa-X está disponível com até 96 núcleos e um total de “1,1 GB” de cache L3. Isso sugere que o chip segue uma configuração semelhante à que vimos no Milan-X do ano passado, com um módulo SRAM de 64 MB empilhado sobre cada CCD.

De acordo com Dan McNamara, vice-presidente sênior de negócios de servidores da AMD, o aumento do cache se traduz em um desempenho 2,2x e 2,9x maior em comparação com os Sapphire Rapids Xeons de 60 núcleos de alta especificação da Intel em uma variedade de dinâmicas de fluidos computacionais e cargas de carga de trabalho de análise de elementos finitos.

Curiosamente, a AMD evitou qualquer comparação com os Max SKUs focados em HPC da própria Intel, que sem dúvida teriam sido a comparação mais apropriada. As peças do Xeon Max da Intel podem ser equipadas com até 64 GB de chip HBM.

No momento da publicação, a AMD não havia divulgado os preços das peças, mas esperamos que eles tenham um prêmio em relação aos Epycs padrão, algo que pode acabar prejudicando seu apelo. Em conversas anteriores com A Próxima Plataformavários fornecedores de HPC têm citado Os altos preços do Milan-X são um problema para os clientes.

AMD revela o sucessor do MI250X

Juntamente com suas novas CPUs, a AMD mais uma vez aproveitou a oportunidade para apresentar sua próxima geração de aceleradores Instinct MI300.

Desta vez, a fabricante de chips confirmou os planos de oferecer pelo menos uma versão do chip em uma configuração somente de GPU chamada MI300X. Com base em declarações de desempenho publicadas anteriormente, esperamos acabar com pelo menos dois X SKUs.

Até este ponto, a maioria das divulgações públicas da AMD foram focado na variante APU do chip, chamada MI300A. A APU está programada para alimentar o próximo Laboratório Nacional Lawrence Livermore o capitão supercomputador e une várias matrizes de CPU, GPU e memória de alta largura de banda em um único pacote.

Em janeiro, a AMD revelou que a APU de 146 bilhões de transistores forneceria desempenho de IA aproximadamente 8x mais rápido, além de obter desempenho 5x melhor por watt do que o MI250X de saída.

O MI300X, revelado esta semana, tem um design mais simples, descartando os 24 núcleos Zen da APU e a matriz de E/S em favor de mais GPUs CDNA 3 e um suprimento ainda maior de 192 GB de HBM3. A AMD observa que isso é grande o suficiente para caber no modelo de linguagem grande Falcon-40B em uma única GPU.

Juntamente com a nova GPU, a fabricante de chips anunciou a AMD Infinity Architecture, que conecta oito aceleradores MI300X em um único sistema padrão projetado com inferência e treinamento de IA em mente. O conceito tem várias semelhanças com o da Nvidia placa-mãe HGXque suporta até oito de suas próprias GPUs.

No entanto, parece que nenhuma variante do MI300 está pronta para estreia pública ainda. A AMD diz que sua APU MI300A já está sendo testada para os clientes, enquanto a versão somente para GPU começará a chegar aos fornecedores em algum momento do terceiro trimestre do calendário.

Novos DPUs a caminho

Por fim, a AMD ofereceu um vislumbre de seu roteiro de rede, que inclui uma nova unidade de processamento de dados (DPU), codinome Giglio, que será lançada ainda este ano.

Se você não se lembra, AMD comprado abriu caminho para o mercado emergente de DPU com a compra de $ 1,9 bilhão da Pensando na primavera passada.

Embora os detalhes sejam escassos, a AMD afirma que seu DPU mais recente, projetado para descarregar tarefas de rede, segurança e virtualização da CPU, oferecerá melhor desempenho e eficiência de energia em comparação com seus DPUs P4 de geração atual.

Os DPUs da empresa já são suportados por vários dos principais provedores de nuvem — Microsoft, IBM Cloud e Oracle Cloud — e pacotes de software como o hypervisor da VMware.

A AMD espera expandir a lista de software compatível antes do lançamento do Giglio no final deste ano com um “kit de desenvolvedor de software em silício” projetado para facilitar a implantação de cargas de trabalho nos DPUs da empresa. ®

.