Enquanto alguns desistiram da Lei de Moore, o CEO da Intel, Pat Gelsinger, claramente não desistiu. “Há décadas, estou no debate: a Lei de Moore está morta? E a resposta é não”, disse ele, durante sua palestra no evento Intel Innovation desta semana.

Apesar de um grande número de opositores, Gelsinger argumenta que há muita vida inexplorada na lei quando trata de design de transistor, fornecimento de energia, litografia e embalagem para 100 bilhões de transistores em um futuro próximo e trilhões de transistores em um único pacote até o final da década.

No núcleo da crença de extensão da vida é a embalagem avançada. De acordo com Gelsinger, e qualquer outra pessoa prestando atenção na fabricação de chips, estamos nos aproximando dos limites do que pode ser alcançado praticamente em uma única matriz. “Mesmo Gordon Moore, quando escreveu seu artigo original sobre a lei de Moore, viu esse dia de acerto de contas onde precisaremos construir sistemas maiores a partir de funções menores, combinando soluções heterogêneas e personalizadas”, disse o executivo-chefe.

A Intel aposta em sua tecnologia de empacotamento e matrizes heterogêneas – colocando diferentes tipos de matrizes em um único pacote de processador, todos conectados internamente – para manter a lei de Moore um pouco mais viva. Você tende a obter melhores rendimentos de fabricação ao fazer muitas matrizes menores, em comparação com as grandes monolíticas, entre outros benefícios.

Isso é exatamente o que, por um lado, a AMD vem fazendo há anos com sucesso e, sem dúvida, ajudou a impulsionar seu rejuvenescimento como fornecedor de chips x86. A AMD vem empacotando vários dies de núcleos de CPU Zen e circuitos de E/S em pacotes de processadores individuais, vendendo-os como seus chips de servidor Ryzen PC e Epyc – os dies, também conhecidos como chiplets, sendo fabricados principalmente pela TSMC e alguns pela GlobalFoundries, dependendo do modelo.

Sem mencionar que a Nvidia e a Apple também estão migrando para os pacotes multi-die, cada um à sua maneira.

O exemplo da Intel. Sua tecnologia de empacotamento multi-die EMIB e Foveros 2D e 3D estará no centro de suas CPUs de servidor Sapphire Rapids e GPUs aceleradoras Ponte Vecchio, embora nenhuma delas esteja disponível comercialmente ainda.

As ambições da Intel para esta tecnologia de embalagem não se limita ao seu próprio silício. A empresa é membro fundadora do consórcio Universal Chiplet Interconnect Express (UCIe) que trabalha para padronizar a maneira como os chiplets de vários fornecedores se comunicam. A UCIe já viu a adesão de alguns dos maiores fabricantes de chips e operadores de fundição, incluindo TSMC e Samsung Electronics.

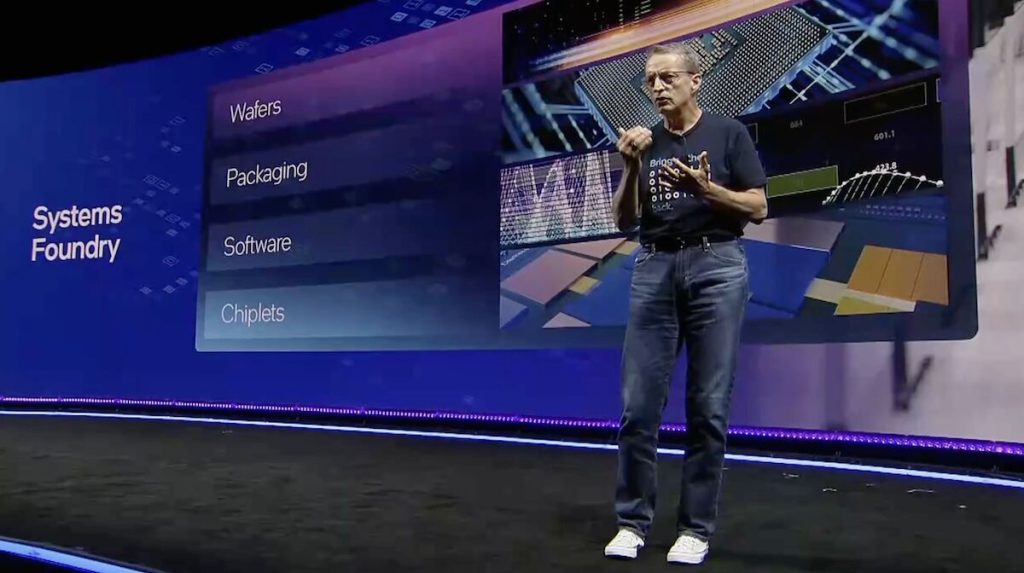

Gelsinger pintou um quadro no qual Intel Foundry Services (IFS) – a fabricação de chips por contrato da empresa braço — iria empacotar chiplets da Intel, TSMC, GlobalFoundries, Texas Instruments e outros em produtos coesos únicos.

- As CPUs de 13ª geração da Intel são quentes, famintas, carregado com núcleos

- Não, ainda não há processadores Intel Sapphire Rapids Xeon para você agora

- Instalação planejada da Intel na Itália agora amarrado na política eleitoral

- Não diga mais Pentium ou Celeron, é apenas Processador agora

A Intel já está fazendo isso até certo ponto com sua plataforma Ponte Vecchio, que usa sua tecnologia EMIB e Foveros para empacotar matrizes fabricadas pela TSMC para suas próximas GPUs de classe de datacenter. E as CPUs Meteor Lake do próximo ano devem usar uma combinação de matrizes TSMC e Intel para a GPU e CPU, respectivamente.

Além disso, Gelsinger vê essa tecnologia de embalagem como um dos serviços de fundição mais atraentes da empresa. “A IFS dará início ao que chamamos de era de fundição de sistemas”, onde o foco muda de sistema em chip para sistema em pacote, disse ele. Na palestra, Gelsinger disse que a Intel estava comprometida com um ecossistema de chiplet aberto. Isso significa que, se alguém quiser usar os chiplets da Intel com a tecnologia de embalagem de outra fundição, o fabricante do chip dará suporte a esse caso de uso. Empresas como LightMatter, Tesla, Cerebras e outras já estão usando técnicas avançadas de embalagem, como a tecnologia chip-on-wafer-on-substrate da TSMC para costurar vários moldes. Portanto, a Intel não tem escassez de concorrência nesta área.

Problema de processo da Intel

É claro que grande parte essa estratégia depende da Intel permanecer competitiva quando se trata de tecnologia de processo. “Você tem que ser uma grande fundição de wafer. Não estamos discutindo isso”, disse Gelsinger, no que parece ser uma alusão à dificuldade da fabricante de chips em trazer seu nó de processo “Intel 4” de 7 nm para o mercado. pandemia, escassez na cadeia de suprimentos e bloqueios, um trimestre sólido para a Intel foi azedado pelas notícias de que falhas foram descobertas no processo de 7nm da fabricante de chips, atrasando seu desenvolvimento em cerca de um ano. E isso foi depois de uma longa e desastrosa jornada chegando até 10nm à produção.

Durante sua palestra esta semana, era o próximo processo 18a da Intel que Gelsinger estava falando. Isso ocorre em parte porque a Intel planeja ultrapassar os 7 nm em um pedido relativamente curto. Supondo que a Intel possa manter seu roteiro de fevereiro, seus processadores cliente Meteor Lake devem estar entre os primeiros a usar a tecnologia de processo há muito atrasada. Mas, para seus chips de 15ª geração, codinome Arrow Lake, a Intel planeja mudar para seu processo 20a, que usa um design de transistor completo. O “a” em 20a significa ångströms, e em 10 ångströms para um nanômetro, que se traduz em 2nm. 18a será um refinamento nesse nó.

A IBM, que a Intel contratou para desenvolver “tecnologias de lógica e embalagem de próxima geração” logo após Gelsinger assumir o cargo de CEO, demonstrou um nó de processo de 2 nm desenvolvido em colaboração com a Samsung no início do ano passado. Se os dois estão relacionados não está claro, mas o desenvolvimento da tecnologia de processo de última geração da Intel está indo bem, de acordo com Gelsinger. Ele afirma que o kit de design de processo para 18a já está nas mãos dos designers de chips, e a fabricante espera gravar os primeiros chips de teste com base no nó antes do final do ano.