.

Se você pensou que o backside power tinha algo a ver com comer muitos vegetais crucíferos, pense novamente: a Intel está implementando isso em chips futuros como uma forma de separar as linhas de energia para os transistores das linhas de sinal, simplificando os layouts dos chips.

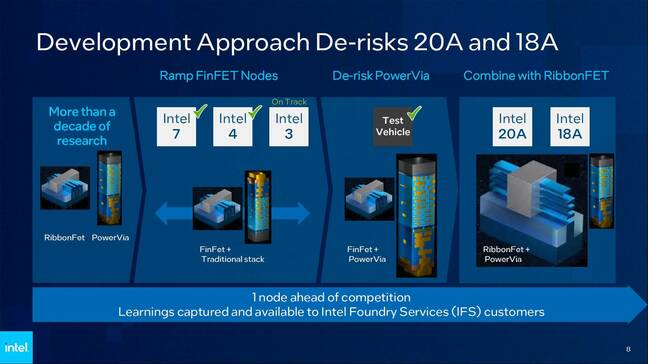

Oficialmente conhecida como PowerVia, essa tecnologia deve estrear em chips produzidos com o nó do processo de produção Intel 20A no primeiro semestre de 2024, seguido pelo Intel 18A, se tudo correr bem.

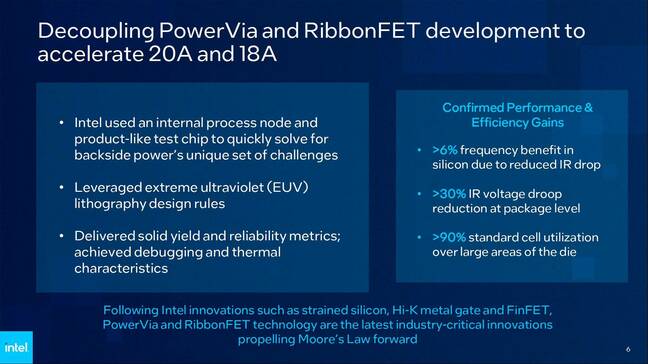

E para ter a maior certeza de que vai dar certo, a empresa construiu e testou a tecnologia por meio de um chip fabricado a partir de um “nó de processo interno” baseado no Intel 4, este último já em produção e em ramp-up para processadores. deve ser lançado antes do final deste ano.

A Intel publicou dois artigos sobre o assunto e disse que apresentará essas descobertas no Simpósio VLSI a ser realizada em Kyoto, Japão na próxima semana.

A entrega de energia traseira é essencialmente apenas colocar as linhas de energia que alimentam os transistores no lado reverso da bolacha de silício da qual os chips são feitos. Implementá-lo, no entanto, não é tão simples.

Essa técnica foi desenvolvida para resolver problemas resultantes do aumento da densidade de chips avançados, como processadores. Estes são fabricados de baixo para cima, começando com os transistores, então camadas de interconexões são adicionadas no topo para criar os circuitos, e isso atualmente inclui as linhas de energia que fornecem eletricidade aos transistores.

O problema é que as camadas de interconexão se tornaram uma teia complexa e confusa que pode começar a afetar o desempenho do chip, de acordo com a Intel, e separar as linhas de energia ajuda a simplificar as coisas.

“À medida que dimensionamos os transistores para obter melhor dimensionamento e melhor desempenho, também precisamos dimensionar todas as camadas de fiação em cima disso. , você começa a ter problemas”, disse o vice-presidente de desenvolvimento de tecnologia da Intel, Bernhard Sell.

“Em primeiro lugar, é muito caro dimensioná-los para dimensões muito pequenas, você precisa usar mais e mais camada UV para padronizar essas camadas. Você também incorre em queda de tensão mais alta devido ao impacto [external connect] até o transistor, porque você começa a passar por linhas e vias de metal cada vez menores, e assim o roteamento do sinal de um transistor para o outro passa por vários fios minúsculos e, se forem muito pequenos, você incorre em um atraso maior”, explicou.

A resposta de acordo com a Intel é mover as linhas de energia para o reverso do wafer, o que libera espaço para a fiação de interconexão.

“Isso tem algumas vantagens. Em primeiro lugar, você obtém contato traseiro muito direto com o transistor, queda de tensão muito baixa, mas também pode relaxar o tom dessas camadas de metal inferiores porque não precisa mais compartilhá-las com os fios de energia”, disse Sell.

A Intel considera que isso torna a fiação de interconexão mais barata de construir e resulta em melhor desempenho. Um ganha-ganha, ao que parece.

Mas a Intel teve problemas amplamente divulgados com novas tecnologias de fabricação ao longo dos últimos anos, problemas que viram a introdução de sua Sapphire Rapids os processadores recuaram várias vezes. A empresa poderia ser perdoada por ser cautelosa.

“Queríamos garantir que você soubesse que aprendemos com o passado”, disse Sell a repórteres durante um briefing, “às vezes introduzimos muitas coisas ao mesmo tempo e tivemos problemas de execução”.

Com o Intel 20A, agora há duas grandes mudanças planejadas: a mudança para RibbonFET do atual design de transistor FinFET e PowerVia. A abordagem tem sido reduzir o risco “separando os que estão fora do desenvolvimento para que possamos garantir que um deles seja totalmente examinado, totalmente desenvolvido e, em seguida, possamos nos concentrar no próximo”, disse Sell.

Essa separação envolveu a construção de um dispositivo de teste baseado em boa tecnologia existente, combinando PowerVia com transistores FinFET para implementar um chip com o codinome Blue Sky Creek usando o design de núcleo de CPU E-core com baixo consumo de energia do próximo Lago Meteoro processador.

“Pegamos o processo FinFET do Intel 4, adicionamos o Nano TSV (através do silício), adicionamos a mesma interconexão de front-end que usamos no Intel 20A e adicionamos todo o processo de rede de fornecimento de energia traseira sobre isso ”, disse Sell.

“Portanto, este é semelhante ao Intel 20A, exceto que possui FinFET em vez de RibbonFET, e nos dá um bom processo de eliminação de riscos; portanto, se isso for bom, tudo o que precisamos focar é no RibbonFET”, explicou ele.

E, de acordo com a Intel, o chip de teste mostrou uma redução superior a 30% na queda de tensão e um ganho de desempenho superior a 6% em comparação com o design de referência Intel 4. A empresa disse que também alcançou uma alta utilização de células de mais de 90 por cento em grandes áreas da matriz, graças às linhas de energia sendo movidas para a parte traseira.

A Intel afirma que será a primeira a implementar a entrega de energia traseira, quando os chips baseados no Intel 20A chegarem ao mercado no próximo ano. Espera-se que isso assuma a forma de Arrow Lake, um próximo processador voltado para PCs clientes.

“Temos muitos casos de uso em IA e gráficos que exigem transistores menores, mais rápidos e mais poderosos, e esse gargalo na fiação estava se tornando um problema cada vez maior”, disse Sell. “Mover os fios de energia para a parte traseira resolve muito dessa preocupação e pode nos levar um pouco adiante para fazer isso”, afirmou. ®

.