.

A Taiwan Semiconductor Manufacturing Co. Ltd., mais conhecida como TSMC, é a maior fundição do mundo. Atualmente, apenas a TSMC e a Samsung produzem chips em massa usando seus respectivos nós de processo de 3 nm (que usam diferentes tipos de transistores, como explicaremos mais adiante). A Apple é o maior cliente da TSMC e acredita-se que seja responsável por um quarto da receita da empresa (isso é 25% para os tipos numéricos).

Com a fraqueza geral da economia global e a ressaca da escassez de chips do ano passado, algumas grandes marcas cancelaram pedidos feitos anteriormente à TSMC. E acredite ou não, isso vale para Maçã também. Você sabe que frequentemente citamos informantes do Twitter e, para fins de aliteração, também verificamos postagens de mídia social de escritores do Weibo. Weibo é um site de mídia social chinês e um assinante, cujo nome de usuário se traduz em algo como @CellPhoneChipExpert (via GizChina) postou algumas grandes notícias da Apple.

A Apple supostamente reduziu seus pedidos de TSMC em até 120.000 wafers

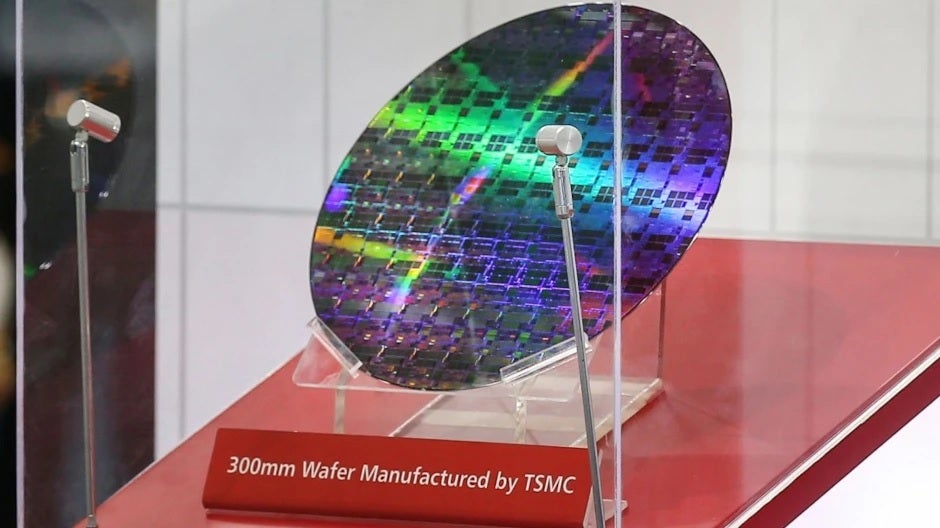

O informante, que supostamente recebe notícias diretamente da indústria de semicondutores, diz que a Apple reduziu seus pedidos com a TSMC em até 120.000 wafers. Os pedidos cancelados eram para chips que seriam feitos usando N7, N5, N4 e até mesmo alguns nós N3 da TSMC. Rumores apontam para o A17 Bionic, que deve ser encontrado sob o capô do iPhone 15 Pro e iPhone 15 Ultra, a ser produzido usando o nó de processo N3 (3nm) da TSMC. Os chips M2 Ultra e M3 da Apple também podem usar o mesmo nó.

Uma bolacha de silício que é usada para produzir chips

O Digitimes relata que a TSMC conseguiu vencer a Samsung Foundry quando se trata de inscrever clientes. O nó de 3 nm da Samsung usa transistores Gate-All-Around (GAA) que permitem que o portão entre em contato com o canal em todos os lados, resultando em menos vazamento de corrente e maior corrente de acionamento em comparação com os transistores FinFET usados pelo TSMC para seu nó de 3 nm. O GAA apresenta nanofolhas horizontais colocadas verticalmente, enquanto o FinFET usa “aletas” verticais colocadas horizontalmente. Espera-se que a TSMC vá para GAA para sua produção de 2nm em 2025-2026.

Apesar de manter o FinFET para produção de 3 nm, a TSMC ainda tem um livro de pedidos bastante completo, com grandes nomes como Qualcomm, MediaTek e Nvidia reservando capacidade de produção para 2023 e 2024. A Samsung, no entanto, foi prejudicada em seus esforços para garantir mais negócios devido a baixos rendimentos. Isso significa que uma porcentagem maior dos cavacos cortados dos wafers falha no controle de qualidade.

Os preços do wafer aumentaram acentuadamente ao longo dos anos

O relatório diz que, para dar à Apple a maior parte da capacidade de produção de 3 nm ainda este ano, a Intel concordou em mudar seu roteiro e atrasar o recebimento de seus pedidos de 3 nm. O nó de processo aprimorado de 3 nm da TSMC (N3E) pode ser lançado este ano, embora possa não haver uma grande pressa para pedidos, considerando o custo.

Digitimes aponta que os preços dos wafers dispararam com wafers de 90 nm sendo vendidos por cerca de US $ 2.000 em 2004. Em 2016, os wafers de 10 nm custavam US $ 6.000 e esse preço atingiu US $ 16.000 por 5 nm, que estreou em eletrônicos de consumo em 2020. Os preços dos wafers para chips de 3 nm estão na casa dos US $ 20.000 área.

A Intel disse que assumirá a liderança do processo da TSMC e da Samsung até 2025, graças a dois desenvolvimentos. Ele usará transistores RibbonFET, que é outro termo para os transistores Gate-All-Around (GAA) já empregados pela Samsung. E usará um recurso conhecido como PowerVia ou entrega de energia traseira. Isso permite que os transistores obtenham energia de um lado de um chip enquanto usam o outro lado para se conectar a links de comunicação de dados.

Os designs de chip de hoje têm transistores tentando lidar com ambas as funções do mesmo lado, o que torna o processo mais complicado e limita o uso de miniaturização. A Intel também será o primeiro a usar litografia ultravioleta extrema (EUV) de alta abertura numérica. Esta máquina gravará padrões de circuitos de alta resolução em wafers, o que pode reduzir o tempo necessário para adicionar recursos adicionais a um padrão.

.