.

Batatas Fritas A Intel usou a conferência Hot Chips desta semana na Califórnia para mostrar um processador de 528 threads com interconexões fotônicas de silício de 1 TB/s, projetado para mastigar as maiores cargas de trabalho de análise, enquanto consome energia.

Para aqueles que esperam um Xeon hiperparalelizado, não é isso. O chip nem é baseado em x86.

Em vez disso, ele foi construído especificamente usando uma arquitetura RISC personalizada para o Hierarchical Identity Verify Exploit (HIVE) da DARPA. programa. Essa iniciativa militar dos EUA procura desenvolver um processador de análise gráfica capaz de processar dados em fluxo 100 vezes mais rápido do que as arquiteturas de computação convencionais, ao mesmo tempo que consome menos energia.

A análise gráfica trata de como os pontos de dados se conectam com outros pontos de dados em sistemas complexos. O exemplo que o principal engenheiro da Intel, Jason Howard, apontou em sua apresentação do Hot Chips foram as redes sociais, que podem executar cargas de trabalho de análise gráfica para entender as conexões entre os membros.

Pense nisso como um Seis Graus de Separação (ou Kevin Bacon) de alto desempenho e você entenderá.

Embora isso possa parecer algo estranho para a DARPA considerar, a agência governamental acredita que a análise gráfica em grande escala tem aplicações no monitoramento de infraestrutura e na segurança cibernética.

Falando em Hot Chips, não perca:

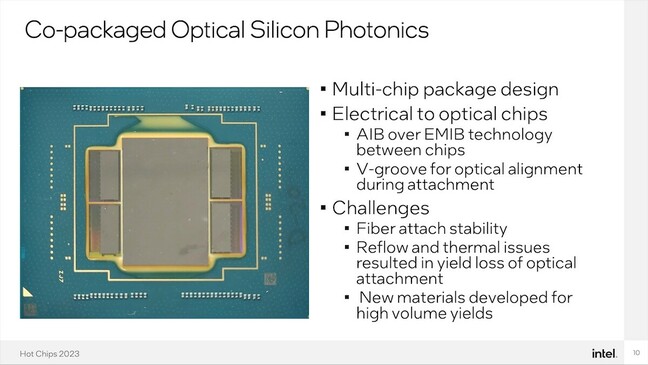

O chip faz parte do primeiro tecido fotônico direto de malha a malha da Intel, que usa interconexões fotônicas de silício para unir vários chips. Mas, em vez de usar cobre para unir dois, quatro ou até oito soquetes usando traços de cobre, a Intel usou óptica co-empacotada para conectar centenas ou até milhares de chips em uma malha de baixa latência e alta largura de banda.

De qualquer forma, essa é a ideia, o chip ainda é um protótipo.

Ampliando a análise gráfica com fotônica de silício

O objetivo é desenvolver tecnologia que possa ser ampliada para suportar até mesmo as maiores cargas de trabalho de análise gráfica.

Os quatro chips ao redor da matriz de computação central fornecem ao protótipo da Intel 1 TB/s de largura de banda óptica – Clique para ampliar

Embora o chip inicialmente pareça ser um processador padrão com alguns bits extras – ele ainda tem uma interface BGA bastante típica, não muito diferente daquelas encontradas nos chips Xeon-D – a maioria dos dados que entram e saem do chip são transmitidos opticamente usando chips fotônicos de silício desenvolvidos em colaboração com Ayar Labs.

Os quatro pequenos chips que circundam a matriz de processamento central convertem os sinais elétricos que entram e saem do microprocessador em sinais ópticos transportados por 32 fibras monomodo. Pelo que entendemos, 16 desses fios de fibra são para transmissão de dados e os outros 16 são para recebê-los.

De acordo com a Intel, cada uma dessas fibras pode transportar dados a 32 GB/s dentro e fora do chip para um total de 1 TB/s de largura de banda. No entanto, Howard disse que nos testes a equipe só conseguiu atingir metade dessa taxa.

Como a Intel prevê, 16 desses chips seriam conectados em rede em uma configuração tudo-para-todos em um único servidor Open Compute Project em seu formato trenó. Então, vários trenós, potencialmente até 100.000, poderiam ser conectados em rede novamente em uma configuração trenó a trenó. O resultado seria que qualquer chip poderia se comunicar com outro, com latências muito baixas, independentemente do sled em que residisse.

Isso não quer dizer que o gigante x86 não tenha enfrentado desafios para fazer a óptica cooperar. Além de atingir apenas metade da largura de banda anunciada, Howard disse que as fibras frequentemente se comportavam mal ou quebravam.

“Depois que tudo estava alinhado e funcionando, havia muitos problemas de fixação de fibras onde elas simplesmente se soltavam porque eram fibras frágeis”, disse Howard. “Também vimos, quando estávamos fazendo o processo de refluxo do pacote geral, que teríamos problemas ópticos devido aos resultados térmicos e acabaríamos tendo rendimentos ópticos ruins”.

Para superar esses desafios, a Intel teve que trabalhar com seus parceiros para desenvolver novos materiais com barreiras térmicas mais baixas, explicou Howard.

Lidando com gargalos de silício

Esse novo sistema era necessário porque, embora o kit comercial atual da Intel acelere as cargas de trabalho de análise gráfica, ele tem dificuldade para escalar.

“Um Xeon pode praticamente pegar um dos conjuntos de dados gráficos e armazená-lo em seu cache e agitá-lo muito rapidamente”, disse Howard, da Intel. No entanto, quando você começa a dimensionar esses conjuntos de dados, você começa a enfrentar gargalos de desempenho e eficiência.

Assim, a equipe decidiu desenvolver um novo tipo de processador otimizado para análise gráfica e rapidamente descobriu várias peculiaridades inerentes à carga de trabalho que poderiam ser otimizadas em silício.

“Vimos imediatamente que eles são massivamente paralelos, na verdade, embaraçosamente paralelos, então poderíamos explorar muito paralelismo para melhorar o desempenho geral”, disse Howard, acrescentando que a equipe também descobriu problemas com a utilização de memória e cache.

“Quando trazíamos uma linha de cache para o processador, normalmente usamos apenas oito bytes dela e acabamos jogando fora os outros 64 bytes sem nunca utilizá-los”, disse ele, explicando que isso colocava uma pressão desnecessária no sistema. vez, havia um monte de grandes pipelines fora de serviço.

Uma parte significativa no centro da matriz é dedicada aos roteadores que controlam o fluxo de dados transmitidos a partir da óptica co-empacotada. – Clique para ampliar

Essas considerações de design levaram a equipe a desenvolver este processador experimental, que a TSMC constrói usando seu processo FinFET de 7 nm (caso você não saiba, a Intel fabrica muitos produtos sem CPU na TSMC e o faz há anos) e que possui oito núcleos cada um com 66 fios.

O chip também usa uma nova arquitetura de memória, uma inclusão importante para otimizá-lo para cargas de trabalho de análise gráfica, explicou Howard. Os chips são emparelhados com 32 GB de memória DDR5 4400MT/s que foi acessada por meio de um controlador de memória personalizado que permitiu granularidade de acesso de 8 bytes. De acordo com Howard, isso foi vantajoso, pois “sempre que retirarmos uma linha de dados da memória, tentaremos utilizar toda essa linha de dados em vez de jogar fora 7/8 dela”.

PCIe 4.0 com conexão 8x permite conectividade de volta ao sistema host.

A Intel também teve que descobrir uma maneira de lidar com o grande volume de tráfego que entra e sai da matriz de computação, que em teoria poderia chegar a 1 TB/s. De acordo com Howard, esse requisito é o motivo pelo qual grande parte da matriz é dedicada aos roteadores.

E embora você possa pensar que tal thread e chip pesado de rede podem esquentar, isso não acontece. O chip atinge 75 watts a 1 GHz. De acordo com a Intel, uma configuração de 16 sleds lidaria com 8 TB de memória, 2.048 núcleos, 135.168 threads e consumiria cerca de 1,2 kW de energia. Isso não é ruim, considerando que um único sistema Sapphire Rapids de soquete duplo com 112 núcleos e 224 threads poderia facilmente consumir tanta energia sob carga.

A Intel imagina que esses chips poderiam ser integrados em plataformas que podem ser dimensionadas para malhas abrangendo 100.000 sleds e alcançar escala de desempenho quase linear até mesmo para as maiores cargas de trabalho de análise gráfica. No entanto, esse sonho continua sendo apenas isso, já que a Intel até agora testou apenas dois chips conectados em sua estrutura.

A comercialização do design pela Intel dependerá de financiamento, explicou Howard. “Se as pessoas quiserem nos dar dinheiro, somos mais que bem-vindos para construir essas coisas.” ®

.